CoWoS(Chip on Wafer on Substrate)是台积电开发的一种先进2.5D封装技术,通过在硅中介层(interposer)上集成多个芯片(如GPU、CPU、HBM等),再将其与封装基板连接,实现高带宽、低延迟的异构集成,已成为高端AI芯片的核心封装方案。

基本概念

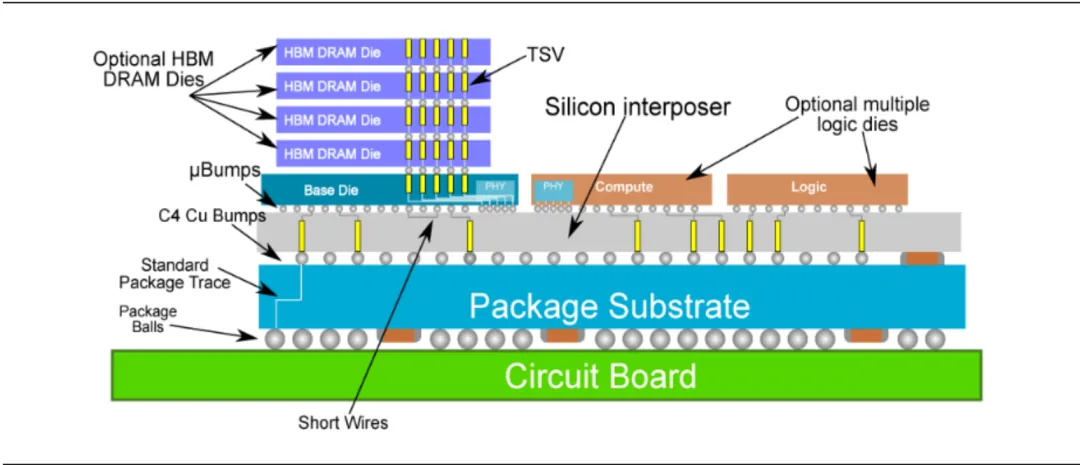

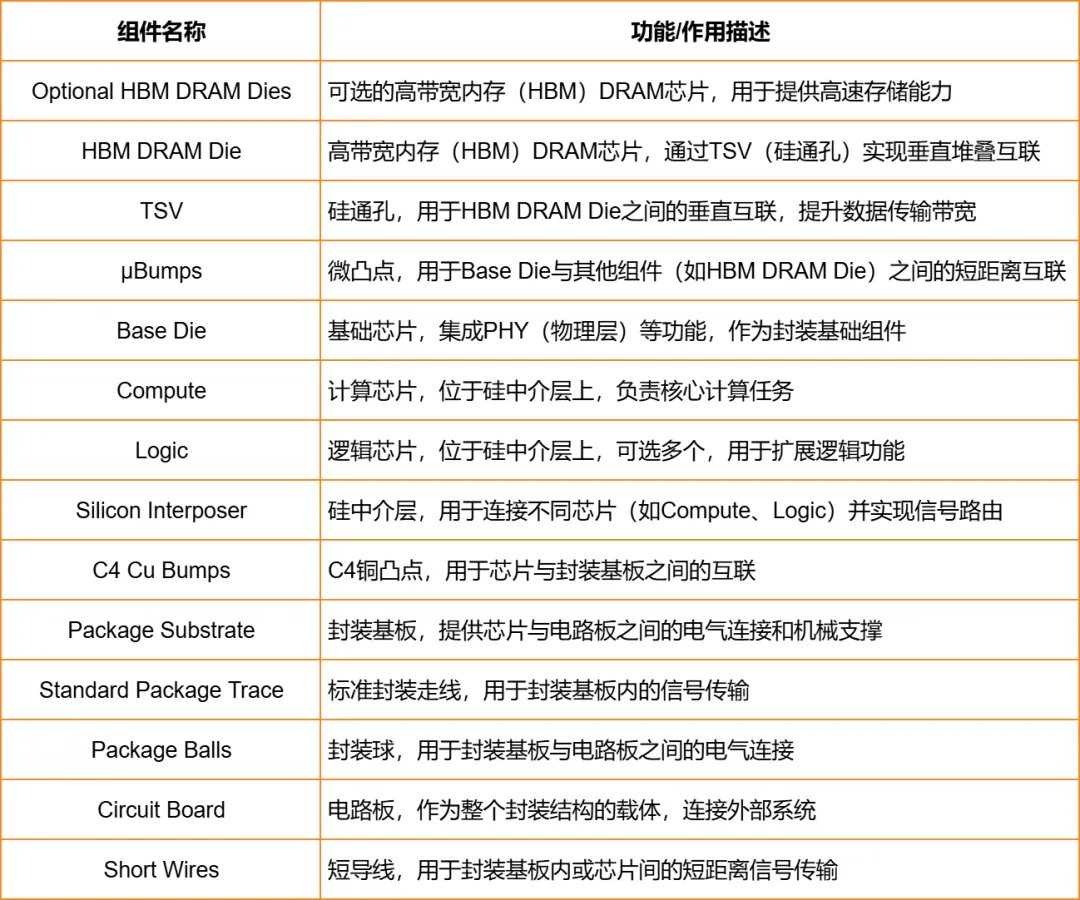

CoWoS封装采用“晶圆上芯片、再置于基板”的三层结构:

底层:为有机或硅基封装基板(Substrate),提供外部电气连接;

中层:为高密度硅中介层(Silicon Interposer),内置硅穿孔(TSV)与微米级布线,实现芯片间高速互连;

顶层:贴装多个计算芯片(如AI加速器)与高带宽存储器(HBM),通过微凸块(Microbump)与中介层键合。

该技术突破传统封装的“内存墙”瓶颈,使芯片间数据传输带宽可达TB/s级别,显著提升AI训练与推理效率。

在半导体领域的应用

CoWoS技术已成为高性能计算(HPC)与人工智能芯片的事实标准,广泛应用于:

AI训练芯片:NVIDIA Blackwell、Rubin等新一代GPU均采用CoWoS封装,支撑大模型训练;

数据中心加速器:谷歌TPU、亚马逊Trainium等ASIC芯片逐步导入CoWoS方案;

高端服务器:用于集成CPU、GPU、DPU的系统级封装,性能较传统方案提升40%,成本降低30%;

技术演进方向:CoWoS-L(将硅中介层集成于封装内)正成为2025年后主流,进一步简化结构、提升良率。

国产替代进展

国内封测企业如长电科技、通富微电、华天科技等已具备2.5D/3D封装能力,正推进玻璃基板、CPO、大尺寸FCBGA等关键技术突破,受益于AI算力自主可控政策,国产先进封装正迎来客户导入窗口期。